Ph.D. Candidate, Cornell University

Email: wl287(at)cornell.edu

Address: 362 Duffield Hall, Cornell University, Ithaca, NY 14853

Phone: 607-227-3943

Wooram Lee received his B.Sc. and M.S. degrees in Electrical Engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea in 2001 and 2003, respectively, and he is currently working toward his Ph.D. degree at Cornell University, Ithaca, NY.

He has held a summer internship at the IBM T.J. Watson Research Center in Yorktown Heights, NY, in 2011, where he worked on a millimeter-wave frequency multiplier in a 90 nm SiGe process. Before joining Cornell, he was a research engineer at the Electronics and Telecommunications Research Institute (ETRI), Daejeon, Korea, where he worked on optical transceivers and links from 2003 to 2007. His research interests include high performance RF IC design, exploiting nonlinear electronics for signal generation and processing in very high frequency and low noise applications.

Awards and Honors

-

IEEE Solid-State Circuits Society Predoctoral Fellowship 2010-2011 (pdf)

-

Best Paper Award in IEEE Workship on Passive Microwave Circuits 2010

-

Best Student Paper Award & Travel grant Award in IEEE RadarCon 2009

-

Samsung Scholarship Foundation Graduate Fellowship 2007-2011

-

Korean Government Overseas Scholarship 2006

-

Best paper Award in 2007 ETRI annual meeting Mar 2007

-

"Rookie of the Year" in 2004 ETRI annual meeting Mar 2004

-

KAIST full scholarship for bachelor's and master's degrees 1997 2003

-

Silver medalist in the National Physics Competition 1996

-

First Prize in Inchon Physics Competition 1996

Research Projects

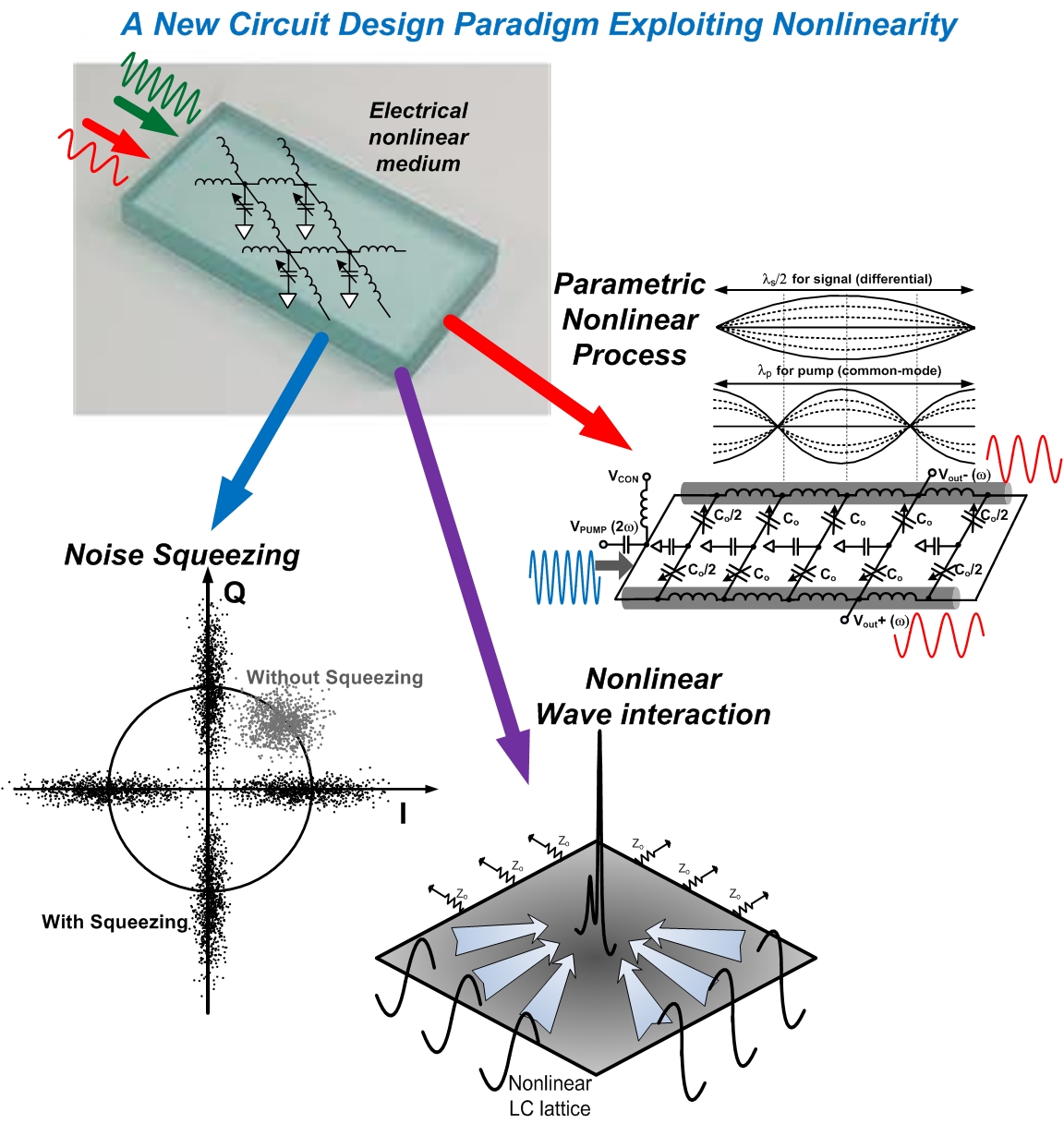

Noise squeezing beyond the thermal noise limit

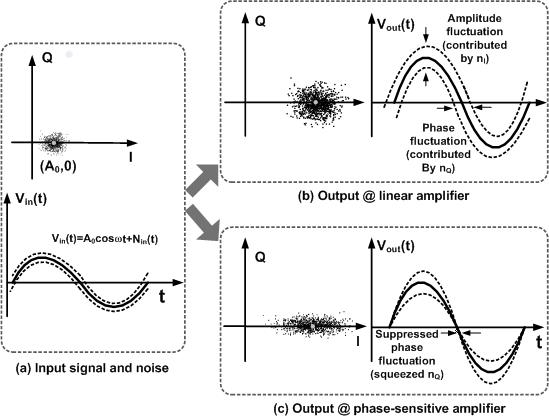

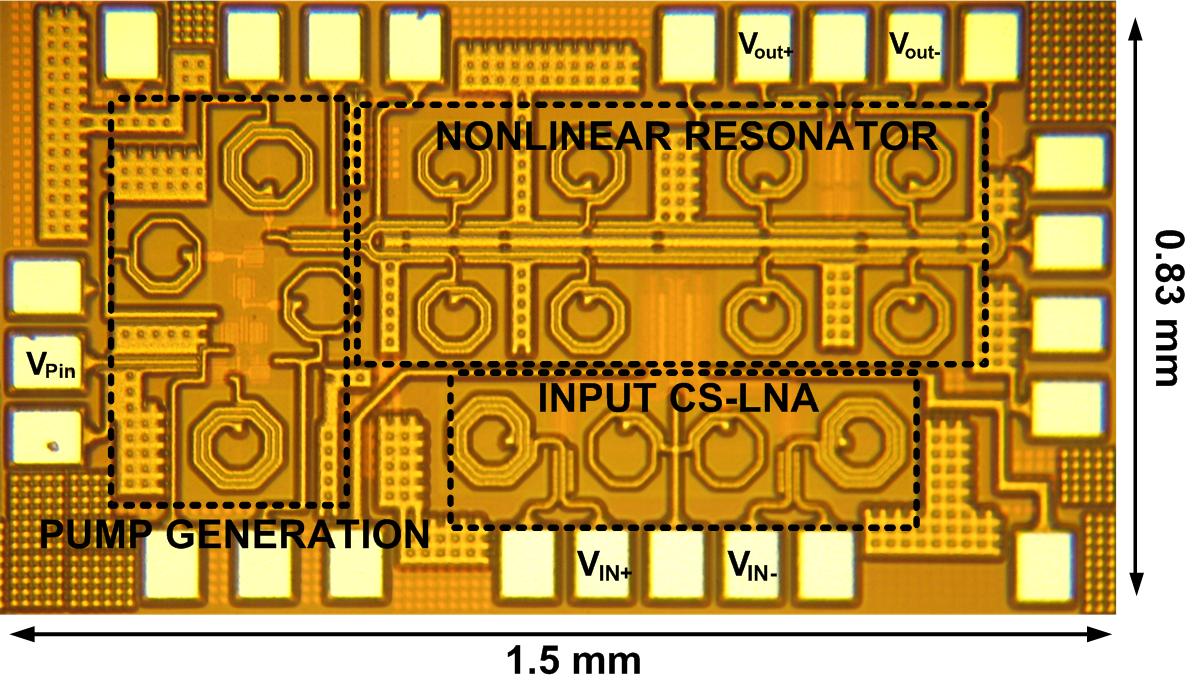

To achieve sensitivity below the thermal noise limit, we demonstrated noise squeezing in electrical circuits for the first time. This concept was originally studied in optics to achieve sensitivity below the limit of the uncertainty principle. We found that we can enhance the sensitivity of one signal aspect (e.g., the phase of in-phase components) at the expense of degrading the other orthogonal aspect (e.g. the amplitude, or quadrature component). The first prototype was a 10-GHz CMOS low-noise amplifier with a sensitivity enhancement factor of 2.5 dB for one quadrature phase. (TCAS2011, MTT2012) Moving forward, we are working on a system of coupled oscillators that can enhance the phase noise by exploiting the noise squeezing effect.

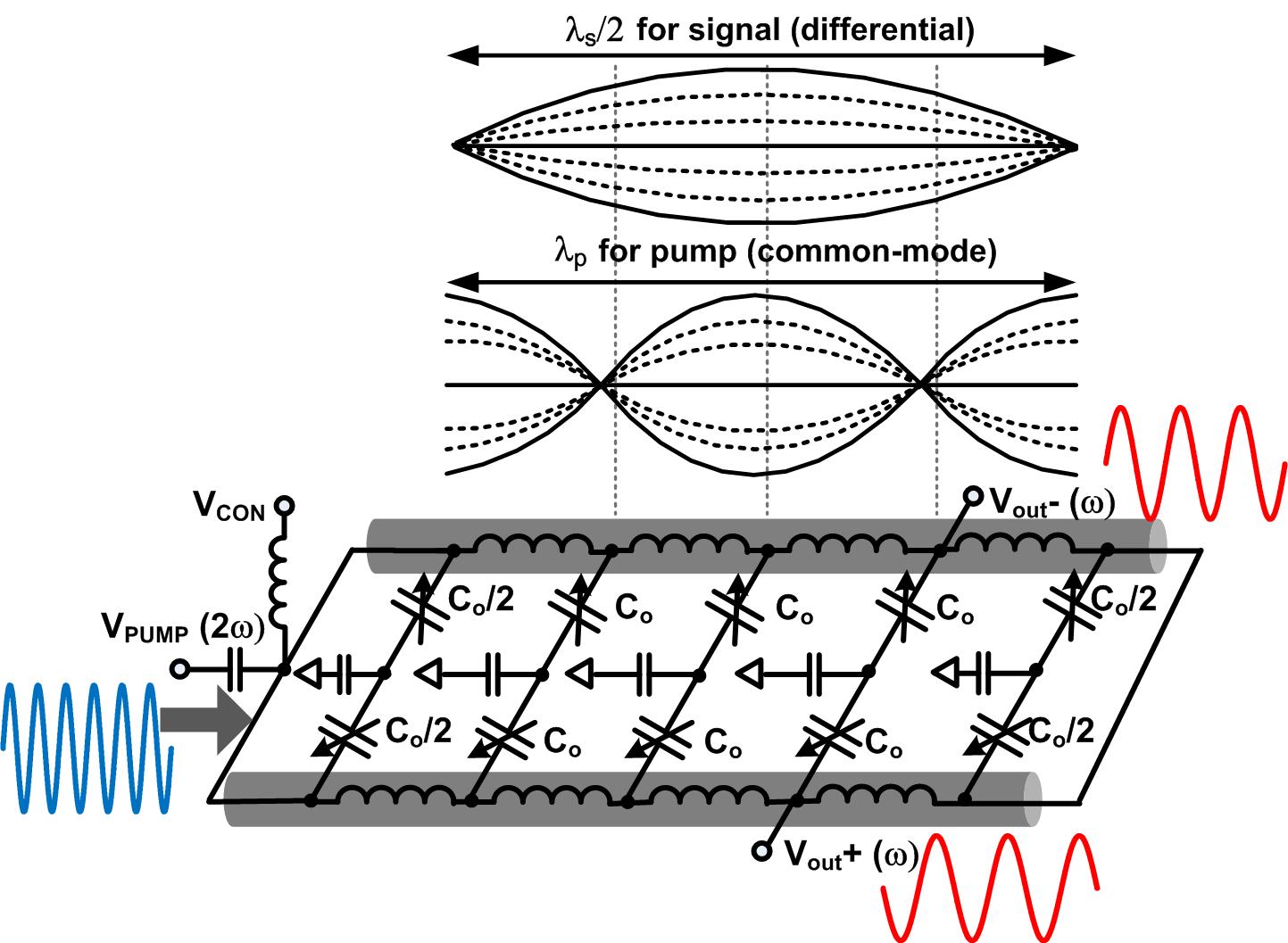

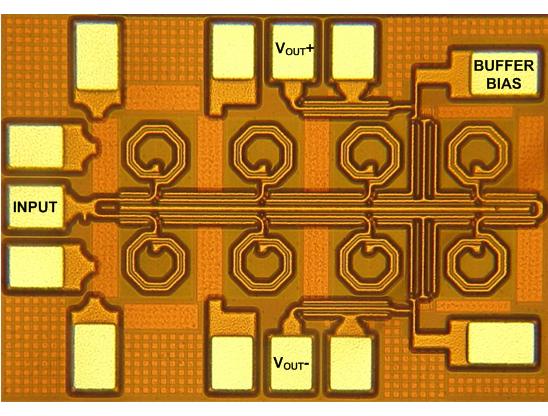

Electrical parametric oscillator: the first passive CMOS frequency divider

To reduce overall system power and phase noise in high-speed frequency synthesizers, we propose an electrical distributed parametric oscillator to realize a passive CMOS frequency divider. Instead of using active devices, which are the main sources of noise and power consumption, an oscillation at half of the input frequency is sustained by the parametric process based on nonlinear interaction with the input signal. To show the feasibility of the proposed approach, we have implemented a 20-GHz frequency divider in a 0.13-um CMOS process. To the best of our knowledge, this is the first passive frequency divider in a CMOS process. (JSSC 2010)

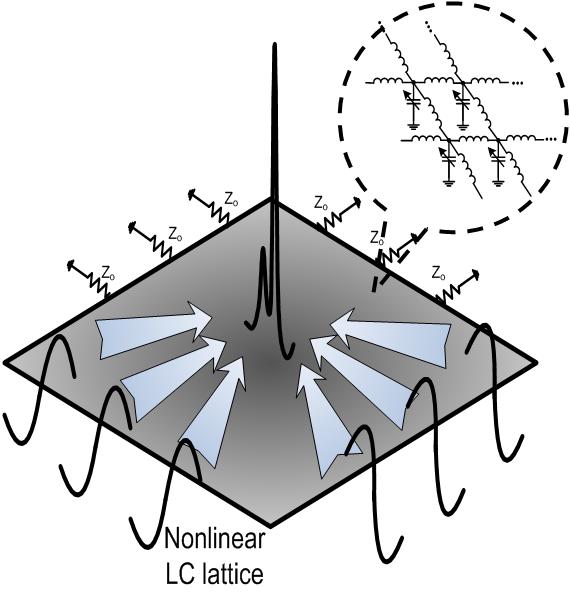

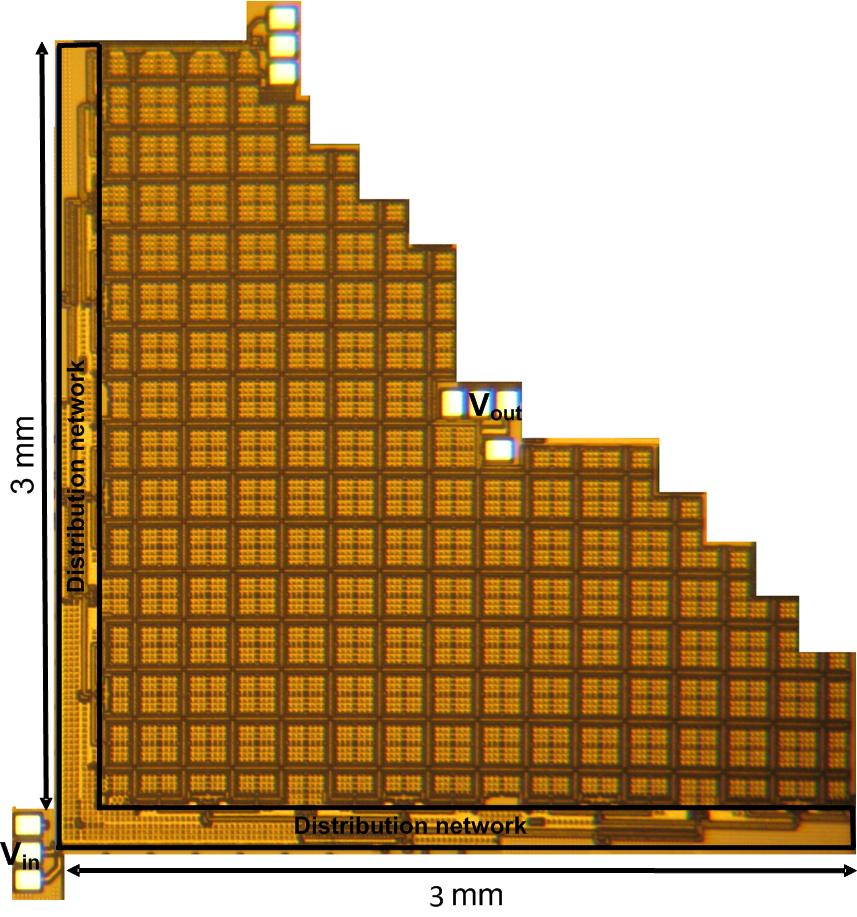

Nonlinear lattice for high-amplitude picosecond pulse generation in CMOS

To go beyond the transistor limits in sharp pulse generation, we use nonlinear wave interaction in a two-dimensional electrical medium. In this system, when two waves collide orthogonally, they combine in a nonlinear fashion: The amplitude of the outgoing wave is greater than the sum of the incoming waves with much higher frequency components. The key is that nonlinearity localizes energy in time and space, resulting in high-amplitude, narrow pulses at the output. After analyzing this concept, we demonstrated 2.7-V pulse generation with a 6-ps pulse width from a 22-GHz input. To the best of our knowledge, regarding the high-amplitude pulses, this work shows the sharpest pulse in any CMOS process. (MTT2012, JPA2010, MTT 2010)

Publications

Publications

Journal Publications:

-

Wooram Lee and Ehsan Afshari, "Fundamental Limits of Harmonic Generation Using Passive Nonlinear Devices," to be submitted.

-

Wooram Lee and Ehsan Afshari, "A CMOS Noise-Squeezing Amplifier," IEEE Transactions on Microwave Theory and Techniques, vol. 60, no. 2, Feb. 2012.

Wooram Lee, Muhammad Adnan, Omeed Momeni, and Ehsan Afshari, "A Nonlinear Lattice for High-Amplitude Picosecond Pulse Generation in CMOS," IEEE Transactions on Microwave Theory and Techniques, vol. 60, no. 2, Feb. 2012.

-

Wooram Lee and Ehsan Afshari, "Low Noise Resonant Parametric Amplifier," IEEE Transaction on Circuits and Systems-I, vol. 58, no. 3, Mar. 2011.

-

Wooram Lee and Ehsan Afshari, "Parametric Distributed Resonator: a Passive Frequency Divider," IEEE Journal of Solid-State Circuits, vol. 45, no. 9, pp. 1834-1844, Sep. 2010.

-

Harish S. Bhat, Wooram Lee, Georgios N. Lilis, and Ehsan Afshari, "Steady-State Perturbative Theory for Nonlinear Circuits," Journal of Physics A: Math. Theor., vol. 43, no. 20, May 2010.

- Georgios N. Lilis, Jihyuck Park, Wooram Lee, Guansheng Li, Harish S. Bhat and Ehsan Afshari, "Harmonic Generation Using Nonlinear LC Lattices," IEEE Transactions on Microwave Theory and Techniques, vol. 58, no. 7, pp. 1713-1723, July 2010.

-

Paul K. J. Park, S. B. Jun, H. Kim, D. K. Jung, W. Lee and Y. C. Chung, "Reduction of polarization-induced performance degradation in WDM PON utilizing MQW-SLD-based broadband source, " Optics Express, vol. 15, issue 21, pp. 14228-14233, 2007 .

-

Wooram Lee, Seung Hyun Cho, Mahn Young Park, Jie hyun Lee, Chulyoung Kim, Geon Jeong, and Byoung Whi Kim, "Frequency Detuning Effects in the Loop-Back WDM-PON Employing Gain-Saturated RSOAs," IEEE Photon. Technol. Lett., vol. 18, pp. 1436-1438, 2006.

-

Wooram Lee, Seung Hyun Cho, Mahn Young Park, Jie hyun Lee, Chulyoung Kim, Geon Jeong, and Byoung Whi Kim, "Wavelength Filter Detuning for Improved Carrier Reuse in Loop-Back WDM-PON," IEE Electron. Lett., vol. 42, pp. 596-597, 2006.

-

Geon Jeong, Jie Hyun Lee, Mahn Young Park, Cheol Young Kim, Seung Hyun Cho, Wooram Lee, and Byoung Whi Kim, "Over 26 nm Wavelength Tunable External Cavity Laser Based on Polymer Waveguide Platforms for WDM Access Networks," IEEE Photon. Technol. Lett. vol. 18, pp. 2102-2104, 2006.

-

Wooram Lee, Mahn Young Park, Seung Hyun Cho, Jie hyun Lee, Chulyoung Kim, Geon Jeong, and Byoung Whi Kim, "Bidirectional WDM-PON based on Gain-Saturated Reflective Semiconductor Optical Amplifiers," IEEE Photon. Technol. Lett., vol. 17, pp. 2460-2462, 2005. (cited 122 times)

-

Jie Hyun Lee, Mahn Young Park, Cheol Young Kim, Seung Hyun Cho, Wooram Lee, Geon Jeong, and Byoung Whi Kim, "Tunable External Cavity Laser Based on Polymer Waveguide Platform for WDM Access Network," IEEE Photon. Technol. Lett. vol. 17, pp. 1956-1958, 2005.

Conference Proceedings:

-

Wooram Lee and Ehsan Afshari, "An 8-GHz, 0.45-dB NF CMOS LNA Employing Noise Squeezing," Radio Frequency Integrated circuits (RFIC) Symp., Jun. 2011.

- Wooram Lee, Farid Amoozear, and Ehsan Afshari, "Picosecond Pulse Generation on CMOS: Design Beyond Transistor Limits," Proc. of IEEE Radar Conference 2009, Pasadena, California, USA. (Best Student Paper Award and Travel Grant Award)

-

Wooram Lee, Seung Hyun Cho, Mahn Young Park, Jie hyun Lee, Chulyoung Kim, Geon Jeong, and Byoung Whi Kim, "Optical Transceiver employing an RSOA with Feed-Forward Current Injection," OFC2007, Anaheim, California, USA.

-

Seung Hyun Cho, Wooram Lee, Mahn Young Park, Jie hyun Lee, Chulyoung Kim, Geon Jeong, and Byoung Whi Kim, "Demonstration of Burst Amplified Uplink for RSOA-based WDM/TDM hybrid PON Systems Using SOA as a Multi-Channel Preamplifier," ECOC 2006, Cannes, France.

-

Wooram Lee, Jaedong Park, and Byoung Whi Kim, "The Performance Analysis of ASE Injection-Locked FP-LD over Injected Light Wavelengths," OECC2004, Yokohama, Japan.

Patents

-

Wooram Lee and Alberto Valdes-Garcia, "Method and Circuits for Bipolar Transistor Frequency Doublers at Millimeter-Wave Frequencies," U.S. patents pending.

-

Ehsan Afshari and Wooram Lee, "Nonlinear Lattice for Picosecond Pulse Generation in CMOS and Methods of Use Thereof," U.S. patents pending.

-

Ehsan Afshari and Wooram Lee, "Distributed Electrical Parametric Oscillator in CMOS Process and Mehods of Use Thereof," U.S. Patent 61/351,964 filed 06/07/2010.

-

Jie Hyun Lee, Mahn Young Park, Geon Jeong, Seung Hyun Cho, Wooram Lee, and Byoung Whi Kim, "Athermal External Cavity Laser," U.S. Patent 2010/0014545, Jan. 21, 2010.

-

Byoung Whi Kim, Wooram Lee, Yun Chur Chung, Eui Seung Son, and Jang Won Chae, "Wavelength Tracking Apparatus and Method in WDM-PON Systems," U.S. Patent 2007/0154216, Jul. 5, 2007.

-

Byoung Whi Kim, Mahn Yong Park, Wooram Lee, Tae Yeon Kim, "Reflective Semiconductor Optical Amplifier (RSOA), RSOA Module Having the Same, and Passive Optical Network Using the Same, " U.S. Patent 2007/0133990, June. 14, 2007.

-

Seung Hyun Cho, Wooram Lee, Jae Dong Park, and Byoung Whi Kim, "Method for Fabricating Laser Diode Having Optical Fiber Bragg Grating as Front Mirror of External Resonator and Laser Diode Fabricated Thereby," U.S. Patent 2006/0133729, June. 22, 2006.

-

Byoung Whi Kim, Wooram Lee, and Jae Dong Park, "Wavelength Tunable Light Source Module for Wavelength Division Multiplexing Passive Optical Network System," U.S. Patent 2006/0098697, May. 11, 2006.